テスト工程

テスト工程 ATPG(Automatic Test Pattern Generation)

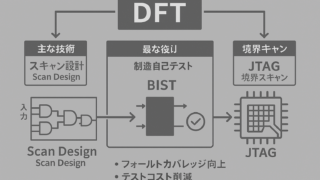

この記事で学べることATPG の目的と背景故障モデル・テストパターン・可観測性/可制御性などの基本概念DFT(Design for Testability)との関係実務での利用シーン(スキャン設計、故障解析、歩留まり改善など)誤解しやすいポ...

テスト工程

テスト工程  テスト工程

テスト工程  テスト工程

テスト工程  テスト工程

テスト工程  テスト工程

テスト工程  テスト工程

テスト工程  技術ニュース

技術ニュース  技術ニュース

技術ニュース  技術ニュース

技術ニュース  技術ニュース

技術ニュース