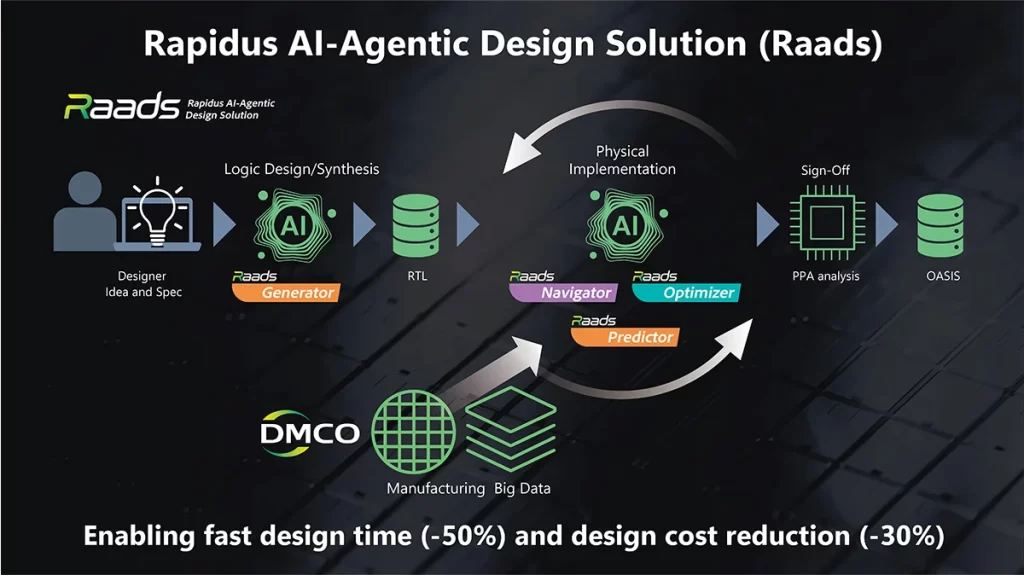

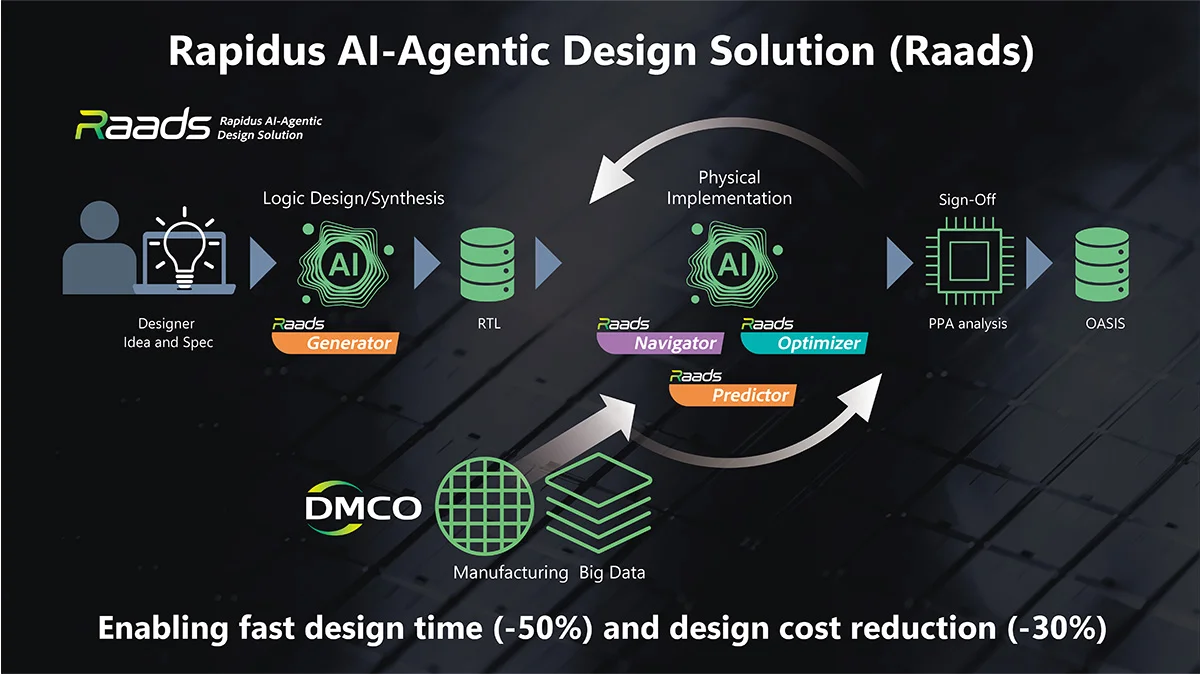

2025年12月17日 – Rapidusは、2nm世代の半導体製造に向けたAI設計ツール群「Raads(Rapidus AI-Agentic Design Solution)」を発表した。LLMや機械学習を活用し、RTL生成からPPA予測、レイアウト最適化までを支援することで、設計期間50%短縮・コスト30%削減を目指す。2026年から順次提供され、同社のRUMS戦略およびIIM-1での2nm量産体制を補完する位置づけとなる。

発表の背景:先端ノード設計の複雑化とAI活用の潮流

2nm世代のロジック半導体では、GAA(Gate-All-Around)構造の採用や設計ルールの高度化により、設計工数・検証負荷が急増している。EDAベンダー各社はAI活用による設計効率化を進めており、TSMCやSamsungもAI駆動の設計フローを強化している。

こうした中、Rapidusは自社プロセスに最適化されたAI設計基盤を提供することで、設計〜製造のサイクルタイム短縮を図り、ファウンドリとしての競争力を高める狙いがある。

発表内容の詳細:Raadsツール群の構成

Rapidusが発表したRaadsは、LLM/MLを活用した複数のEDAツールで構成され、PDKやリファレンスフローとセットで提供される。

https://www.rapidus.inc/news_topics/news-info/rapidus-unveils-new-ai-design-tools-for-advanced-semiconductor-manufacturing/

Raads Generator(LLMベースのRTL生成)

- 仕様を入力すると、Rapidusの2nmプロセスに最適化されたRTLを自動生成

- 設計初期段階のコード作成を大幅に効率化

Raads Predictor(PPA予測・RTLデバッグ)

- RTLとSDCを入力すると、短時間でPPA(Power/Performance/Area)を予測

- 物理設計を意識したRTL最適化を支援

2026年以降に提供予定の追加ツール

- Raads Navigator / Indicator:設計QA支援、設計課題の解決支援

- Raads Manager:ML/AIによるレイアウト階層構成の最適化

- Raads Optimizer:PPA最適化パラメータの自動探索

これらのツールは、従来のEDAツールと併用することで設計期間50%短縮、設計コスト30%削減を可能にするとしている。

技術的ポイント:2nmプロセスとAIエージェント設計

2nm GAAプロセスへの最適化

RapidusはIIM-1で2nm GAAトランジスタの試作を進めており、電気特性の取得も開始している。

GAAはFinFETよりもゲート制御性が高く、微細化に適した構造であるため、PPA最適化の自由度が増す一方、設計ルールは複雑化する。

Raadsはこの複雑性をAIで吸収し、設計者の負担を軽減する。

AI-Agentic Designの特徴

従来の「AI-Assisted」から「AI-Agentic」へとコンセプトを進化させ、AIが能動的に設計課題を解決するアプローチを採用。

例:

- RTL生成 → PPA予測 → 最適化案提示

という一連の流れをAIが主導し、設計者はレビューと意思決定に集中できる。

PPA最適化の高速化

Raads PredictorとOptimizerにより、PPA探索の反復回数を削減し、物理設計前の段階で最適化の方向性を把握できる。

これは、2nm世代で特に重要となる配線遅延・IR drop・セル密度のトレードオフ検討を効率化する。

ビジネス的ポイント:ファウンドリ競争と顧客メリット

顧客メリット

- 設計期間50%短縮、設計コスト30%削減

- PDKとAIツールが統合された専用フローにより、先端ノード設計の参入障壁を低減

- 中小企業やスタートアップでも先端プロセスを扱いやすくなる可能性

ファウンドリとしての競争優位性

RapidusはTSMCやSamsungに比べて量産実績では遅れを取るが、「設計〜製造の一体最適化」

を武器に差別化を図る戦略を採用している。

特に、IIM-1で採用されている全工程枚葉処理(Single Wafer Processing)は、詳細なプロセスデータ収集に適しており、AIモデルの精度向上に寄与する点が特徴的。

今後の展望:AI設計と先端製造の融合

- 2026年以降、Raadsツール群が順次リリースされ、2nm量産に向けた設計エコシステムが整備される見込み。

- AIエージェントによる設計自動化は、EDA業界全体のトレンドであり、Rapidusの取り組みはその一部として位置づけられる。

- 長期的には、Raadsが外部EDAツールとの連携を深めることで、より広い設計コミュニティに浸透する可能性がある。

- 日本国内の半導体産業再興において、設計効率化は重要な要素であり、Raadsはその基盤技術として期待される。

コメント