システムの複雑化により、マルチクロック、マルチリセットの設計が増加している。

しかし、異なるクロックドメイン、リセットドメイン間のデータの受け渡しは注意が必要となる。RTLシミュレーションと実機で挙動が異なり、意図しない動作を引き起こすためである。

また、この現象はごくまれに発生するため、実機での原因の特定は困難を極める。そのため、問題が発生する回路を設計しないことが重要となる。

本コラムでは、非同期回路設計における問題点とその対策について説明する。

CDC(Clock Domain Crossing)

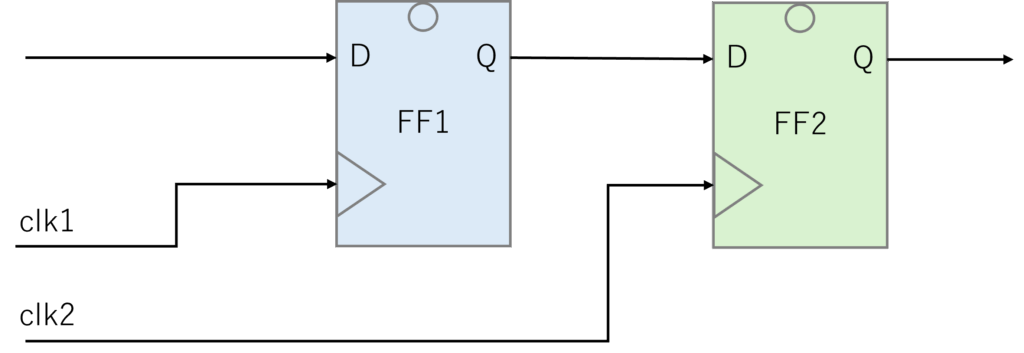

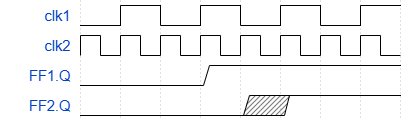

異なるクロックドメインのFFのデータの受け渡しは、RTLシミュレーションと実機で異なる挙動を引き起こす。

RTLではレースコンディションを除いて、クロックイベントによりFF出力は即時に遷移する。しかし、実機はクロックイベントが発生すると、不安定な状態を経て、値が確定する。この不安定な状態をサンプリングすると、そのFFの出力も不安定な状態となる(メタステーブル)。

メタステーブルにより出力は安定しないため、意図しない動作を引き起こす可能性がある。

この現象はごくまれに発生するため、実機で原因を突き止めることは非常に困難である。

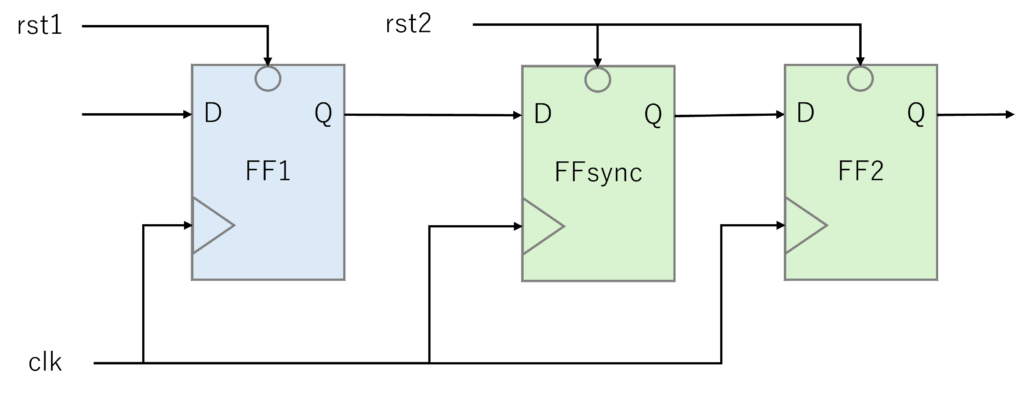

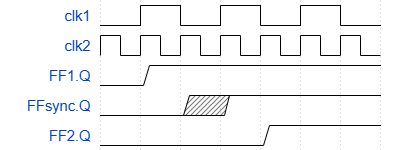

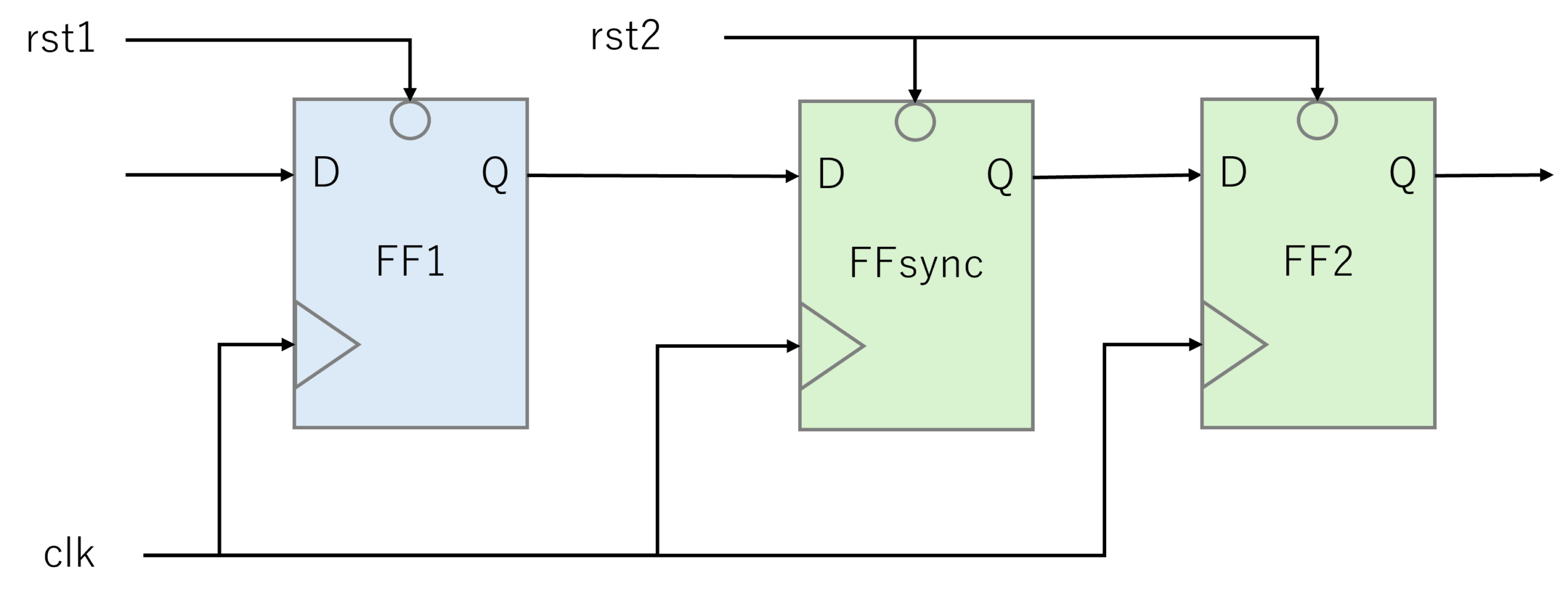

シンクロナイザの挿入

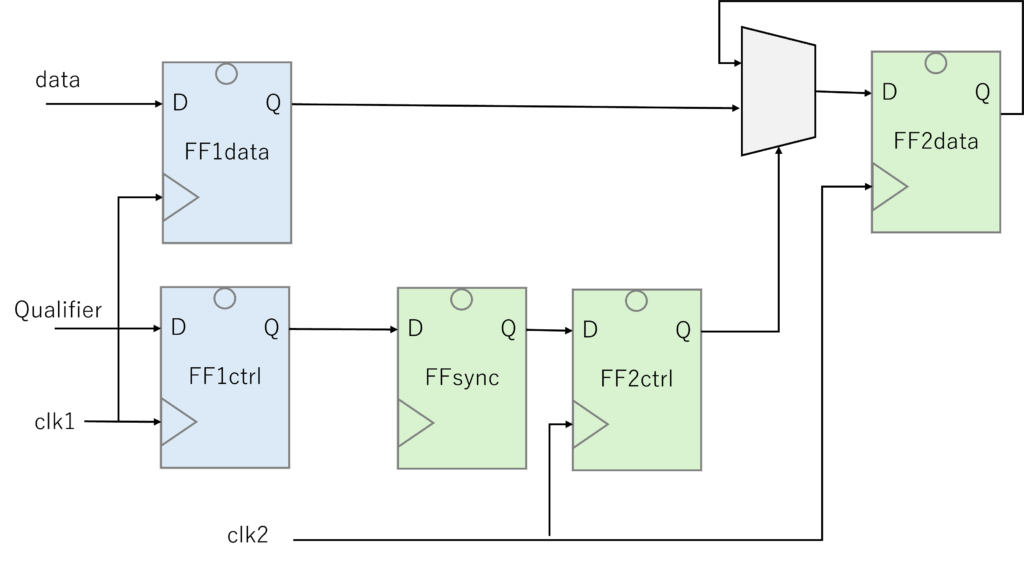

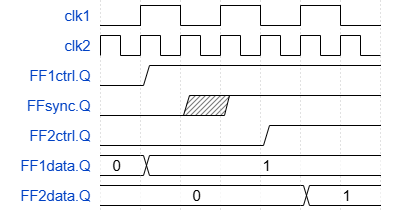

FF1とFF2の間にシンクロナイザ(FFsync)を挿入する。FF1.QのメタステーブルはFFsyncで値を確定させる。よって、FF2.Qはメタステーブルではなくなるため、回路動作は安定する。

D-MUX

複数ビットの信号(データ)は、実際の回路では遅延により、FFに到達するまでの時間がビットごとに異なる。

シンクロナイザで同期化すると、このビットごとの遅延のばらつきにより、所望のデータをサンプリングできない可能性がある。

そこで、D-MUXで同期化する。D-MUXでは、ソース側のEnable信号をシンクロナイザで同期する(Qualifier)。Qualifierがアサートしたあとのデータをサンプリングすることで、安全にデータを送信する。

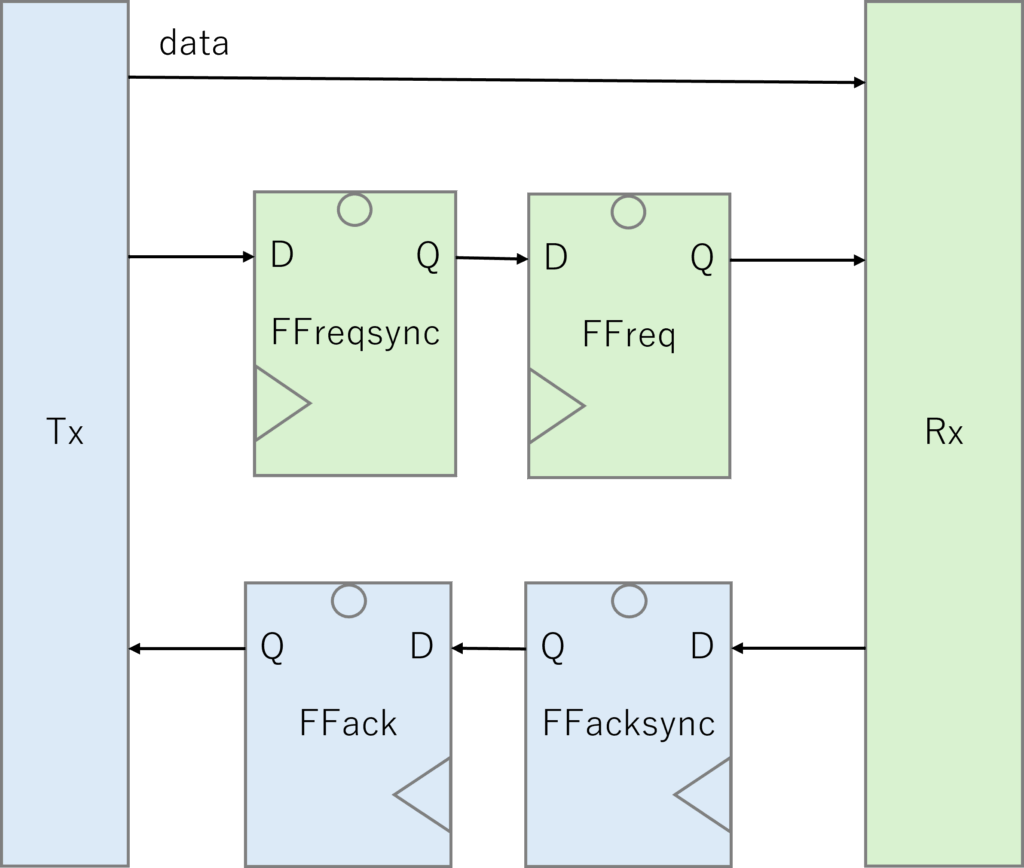

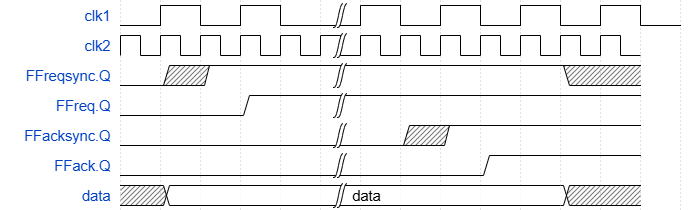

ハンドシェイク

REQ/ACK信号により同期をとる。

送信側がREQ信号をアサートしてデータを送信する。受信側がREQ信号を受け取り、データを受け取るとACKを返す。送信側がACKを受けたらREQをデアサートする。

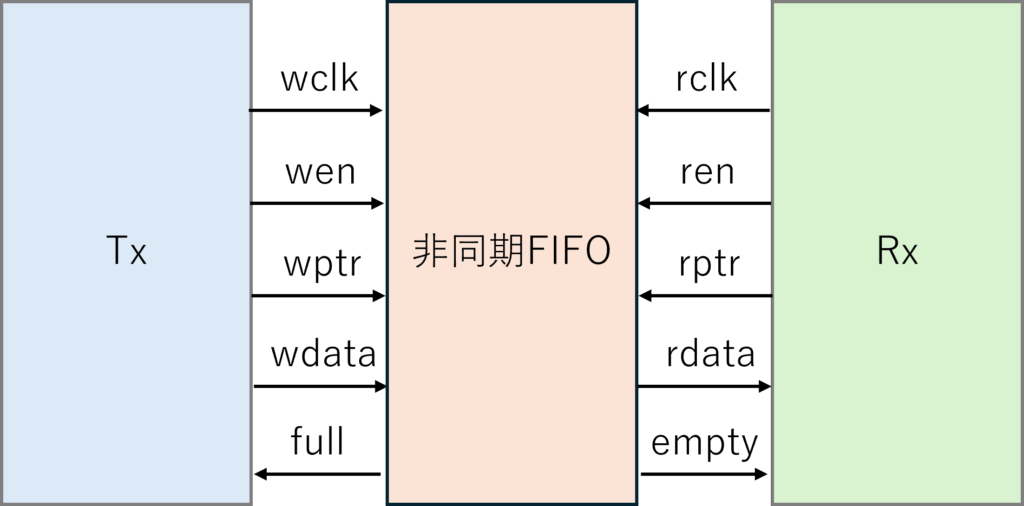

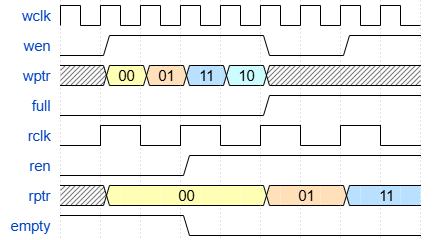

非同期FIFO

FIFOを介してデータを送信する。

送信側はFIFOを介してメモリにWriteする。受信側は書き込まれた値をFIFOからReadする。

アドレスはグレイコードに変換してシンクロナイザを介して同期をとる。

RDC(Reset Domain Crossing)

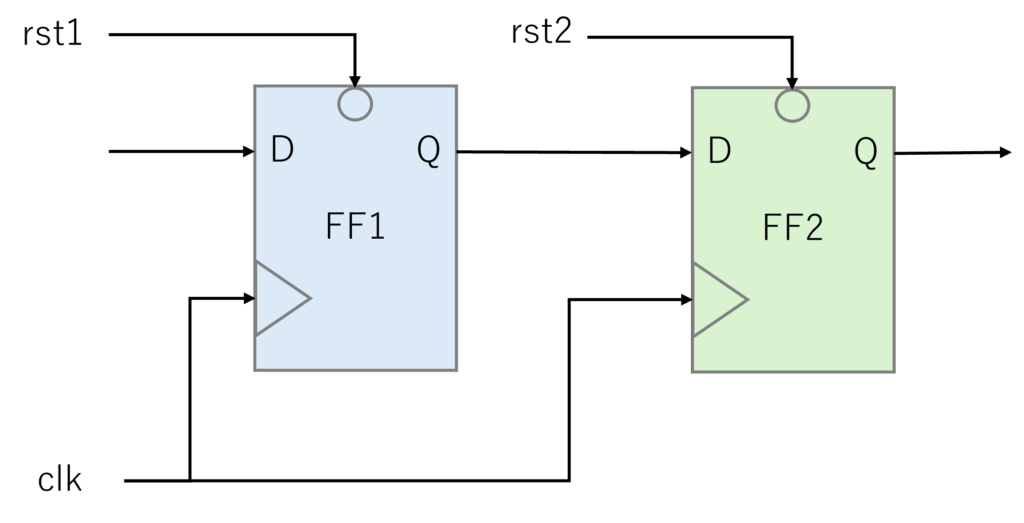

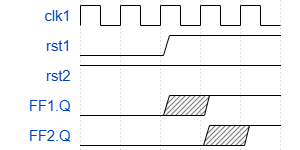

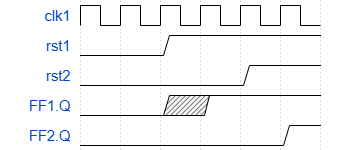

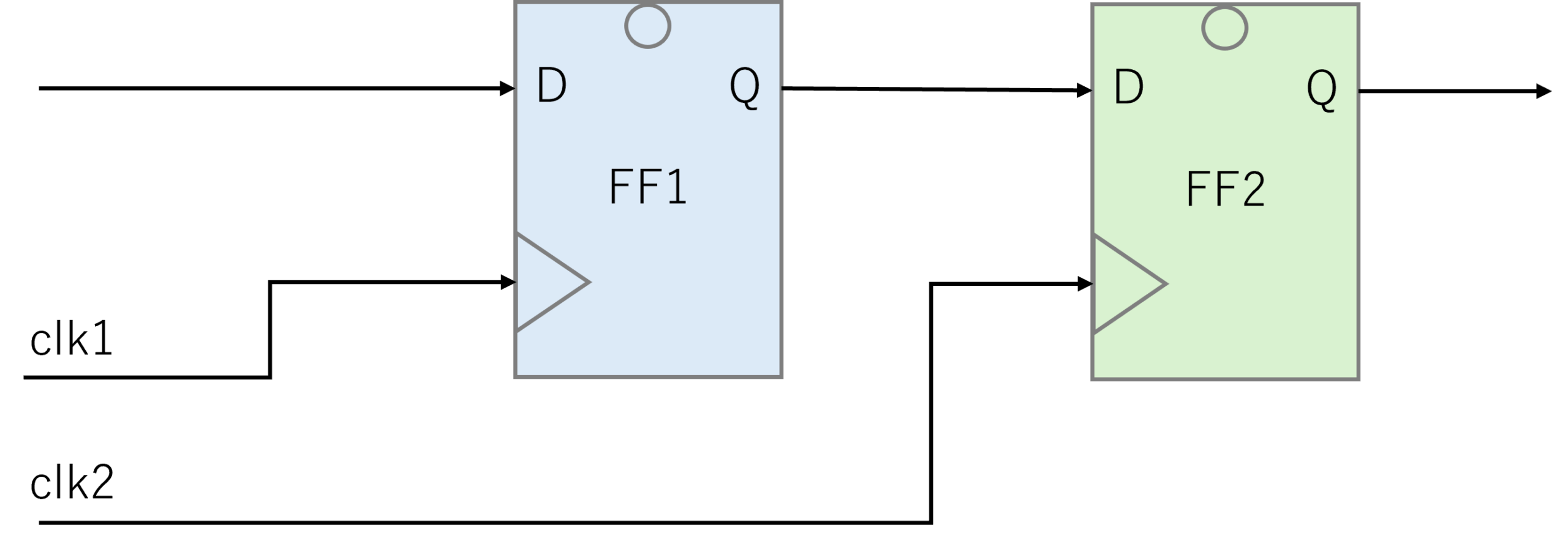

非同期リセットrst1でリセットされるFF1と非同期リセットrst2でリセットされるFF2でデータを受け渡している回路がある。

この回路ではrst1->FF1.Q->FF2.DでRDCパスが形成されており、FF2.Qでメタステーブルが発生する恐れがある。

図において、rst1のデアサートとクロックが近接すると、FF1.Qはメタステーブルになる。このとき、rst2がデアサートされていると、その影響はFF2.Qにも伝播する。

リセットオーダリング

非同期リセットrst2をデアサート後に非同期リセットrst1をデアサートする仕様にすることで、rst1->FF1.Q->FF1.DのRDCパスによるメタステーブルを防ぐことが可能になる。

シンクロナイザの挿入

CDC同様にシンクロナイザを挿入することで、メタステーブルの伝播を防ぐことが可能となる。

リコンバージェンス

メタステーブルが発生しないように非同期対策を行っていても、さらなる注意が必要となる。

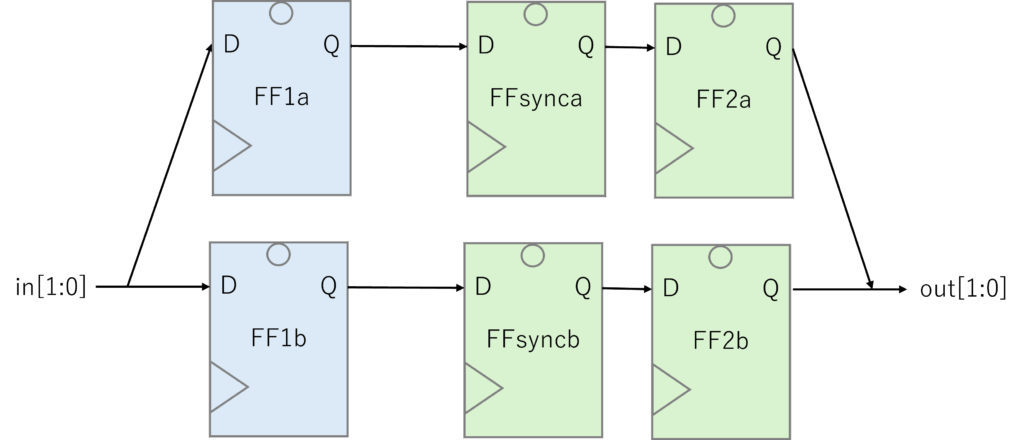

例えば、下図のように2ビットの信号をシンクロナイザで同期した回路がある。

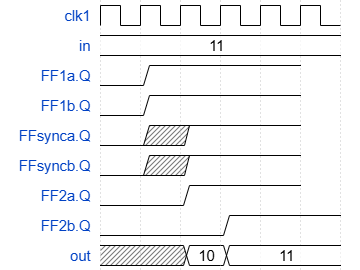

in[1]とin[0]はそれぞれシンクロナイザで非同期対策を行っている。RTLシミュレーションでは、FF2a.QとFF2b.Qの出力は揃っているが、実回路においては遅延量が異なり、変化タイミングが1サイクルずれることがある。

これにより意図しない動作を引き起こす可能性がある。この問題はリコンバージェンスと呼ばれている。

リコンバージェンス構造を作らない

複数ビットの信号を異なるクロックドメインに送信する場合はD-MUXはハンドシェイクを使用する。どうしてもリコンバージェンス構造になる場合は設計仕様として、信号が安定したあとにサンプリングするように定義する。

グリッチクロック

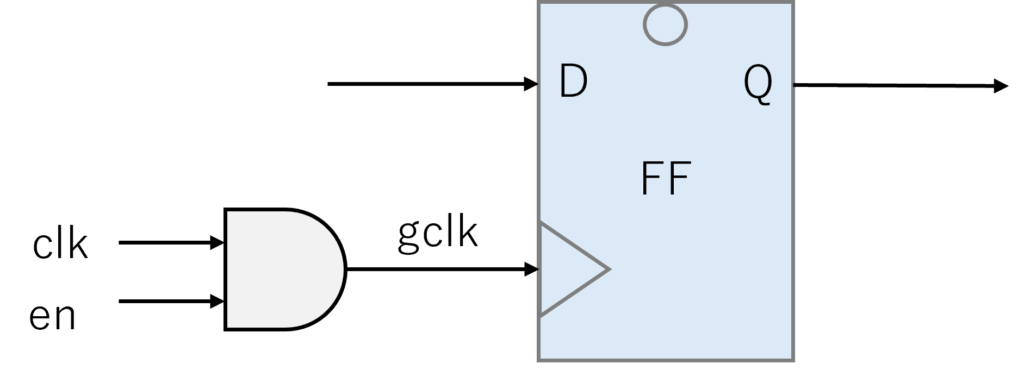

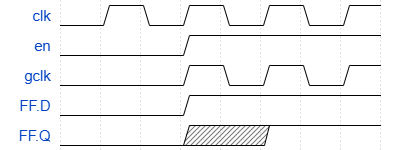

クロックゲーティングにおけるEnable信号がクロックがHighの状態で変化することで発生する。

CGC(Clock Gating Cell)の使用

Enable信号が非同期で変化することで、クロックがHighの状態で変化する恐れがある。そのため、Enable信号はゲーティングするクロックに対して同期させる。

また、クロックゲーティング論理は専用セル(CGC)を用いるのが一般的であり、FPGAではマクロが用意されている。

リセット解除グリッチ

クロックゲーティングのEnable論理が非同期リセット信号によって初期化されるかつ、クロックが動作しているときにリセット解除すると、グリッチが発生する可能性がある。グリッチが発生することで、意図しないサンプリングが行われ、不具合の原因となる。

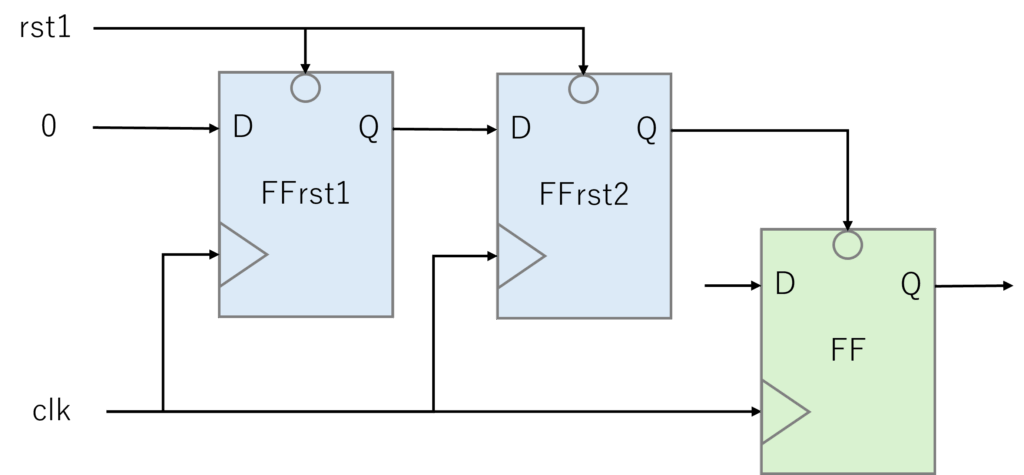

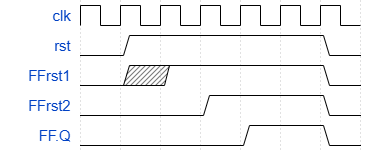

非同期リセットの同期化

非同期リセットのデアサートを同期化する。同期化することで、クロックイベントでEnable信号がアサートするため、グリッチの発生を防げる。

参考

コメント